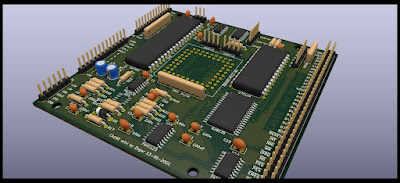

Klon CA80 - omówienie schematu.

Największą zmianę w stosunku do oryginału możemy znaleźć w dekoderze adresów pamięci. Podział na szesnastokilobajtowe obszary pozostał, jednak zastosowany RAM ma 128 kB, więc może pokryć wszystkie.

|

| Dekoder adresów pamięci. |

Za pomocą zworek na J4 (ROM_SEL) możemy wybrać adres Epromu w U9. Wejścia U1D są podciągnięte do +5V, więc bez zworek ROM_CE_ zawsze będzie w stanie wysokim ("podłoga" na końcu nazwy oznacza aktywny stan niski sygnału), czyli U9 nie będzie wybierana. Cała przestrzeń adresowa będzie zajmowana przez 64 kB RAM (reszta jest niewykorzystana). Druga zmiana to sygnał MEM_EN. Jest to odpowiednik RAM_CE2 z Z80-MBC2. Zmieniłem mu nazwę, bo będzie on blokował dostęp do każdej pamięci, nie tylko RAM.

Modyfikacje ZS są zgodne z opisem w MIK. ZS38 pozostawał wolny, więc podłączyłem go do BUSRQ_. Wyjątkiem jest MEM_EN, który użyłem zamiast ZC/TO1 (ZS37). W przypadku podłączenia oryginalnego MIK89 należy o tym pamiętać, bo powinien tam dochodzić sygnał 1 kHz, przewidziany do generowania NMI_ "w przypadku trudności ze zdobyciem MCY74518". Trudne czasy minęły, więc możemy śmiało z tego zrezygnować. Poza tym w klonie w/w układ nie występuje. Nie ma dzielnika częstotliwości, nie ma nawet generatora! Nie ma też elementów RC dla resetu. Jak żyć?

Analogicznie do rozwiązań z Z80-MBC2 zarówno CLK, jak i NMI oraz RESET_ są generowane przez ciało obce - Atmegę. Ten sposób sterowania procesorem jest bardzo skuteczny. Możemy tak dobrać czasy, że start procesora nastąpi w sposób książkowy - nie będą potrzebne cztery NOP-y na start (oczywiście, zgodnie ze wstępnym założeniem, pozostaną na swoim miejscu).

Po co ta Atmega? Zdecydowanie jest nieoceniona. Poza generowaniem CLK, NMI i RESET_ (co bardzo upraszcza schemat, a co za tym idzie rozmiar PCB) umożliwia bezpośredni (prawie) dostęp do pamięci CA80. W czasie rozruchu możemy wypełnić ją dowolnym programem lub danymi. Te dane mogą być zapamiętane we flash-u Atmegi, na karcie pamięci SD a nawet w EEPROM-e w module RTC. Co prawda w module jest AT24C32 czyli 4 kB, ale łatwo można go wylutować i zastosować większy (sprawdziłem doświadczalnie). Możemy na koniec wpisać aktualny czas!

|

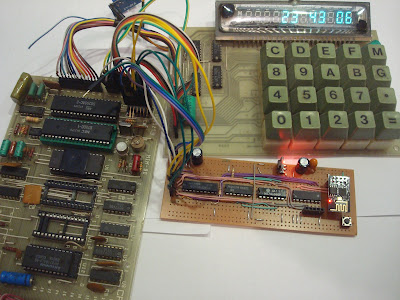

| Kanały: 1. CLK, 2.MEM_EN, 3.SNMI_ |

Jak to działa? Początkowo nasz Z80 zostanie ubezwłasnowolniony. Sygnał CLK będzie precyzyjnie reglamentowany. Program działający w Atmedze będzie ustawiał sygnały, symulując pracę systemu. W tej fazie wystarcza dostęp do szyny danych CLK i RESET_. Odmierzamy czas niezbędny do prawidłowego zerowania procesora, po czym kończymy reset. Od teraz każdy takt CLK jest liczony. Na szynę danych w M1 (fetch) jest podawany kod rozkazu. Potem wartości ewentualnych parametrów. Z80 pracuje tak, jakby korzystał ze swoich zasobów, jednak czyta sygnały podawane na szynę danych z zewnątrz. Wykorzystano rozkazy LD HL,nnnn - wskaźnik pamięci do której będziemy pisać, LD (HL),nn - wpisanie danej pod adres wskazywany przez HL oraz INC HL - inkrementacja wskaźnika. W zależności od cyklu maszynowego procesora ustawiany jest sygnał MEM_EN. Po przesłaniu wszystkich bajtów (w różne obszary) należy przeprowadzić reset procesora, w czasie którego uruchomimy timer w Atmedze generujący CLK 4 lub 8 MHz. Po zakończeniu resetu procesor ruszy od adresu 0, czyli zacznie pracę jako CA80. Będzie już miał ustawiony zegar i wgrany dowolny program do przetestowania lub do wykonania. Proste? Do tego bardzo szybkie. Po zmianach w kodzie (w Z80-MBC2 CLK i inne sygnały były generowane za pomocą arduinowych DIGITALWRITE, co było bardzo powolne) na operacje na rejestrach, przesłanie 8 kB (cały EPROM) zajmuje 150 milisekund. To czas niezauważalny gołym okiem. Włączamy zasilanie i od razu widzimy "CA80" na wyświetlaczu.

Wyżej opisany sposób jest dobry, ale ma ograniczenia. Można go stosować tylko do procesorów statycznych. W dodatku muszą być w 100% zgodne z oryginalnym Z80. A gdyby użyć Z180? Przecież jest oryginalny. Niestety nie jest w pełni zgodny z poczciwym starszym bratem! Jest szybszy. I nie chodzi tu o częstotliwość CLK! Niektóre cykle maszynowe mają inną długość - zamiast czterech trzy takty. Musielibyśmy przeliczyć wszystko od początku... Poza tym Z180 dzieli CLK przez 2 i działa na sygnale PHI i niestety ten sposób się nie sprawdził. Można było dojść do ładu wysyłając na początek kilka NOP-ów, ale niestety nie za każdym razem dawało to zamierzony efekt. Wpadłem na genialny (moim zdaniem) pomysł, żeby od razu podać stabilne CLK i nie przejmować się szczegółami. Wstrzymywać pracę procesora sygnałem WAIT_, kiedy będzie to potrzebne. Wystarczyło zmienić koncepcję zastosowaną już w Z80-MBC2 i zamiast IORQ_ wykorzystać RD_. Dzięki temu nie tracimy czasu na drugi reset (po przesłaniu danych do RAM) i dostajemy nową możliwość - wykonywania dowolnych rozkazów. Możemy np. użyć JP nnnn i rozpocząć pracę systemu w innym miejscu (na przykład skonfigurować coś przed ruszeniem monitora).

Nowe możliwości otworzyły drogę do dalszych posunięć: Budowę klona z procesorem Z180 i opracowanie uproszczonego emulatora MIKSID. Ale o tym później.

Komentarze

Prześlij komentarz